- 供給業者とJEDECは、予測されるGen AIブームを疑って、NvidiaのGPUがそれを早急に必要とすると考え、HBM4計画を前倒しにしている。

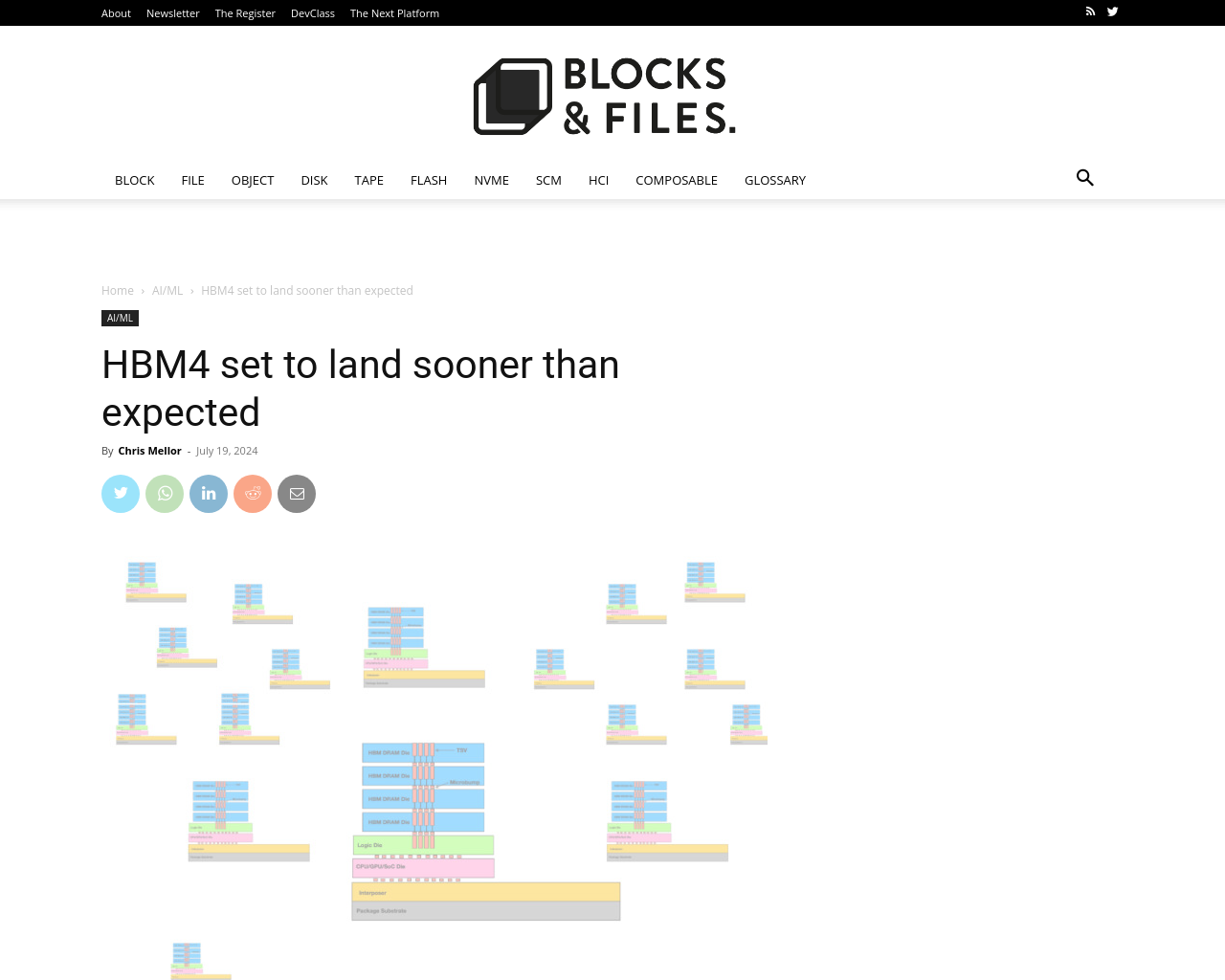

- HBM(High Bandwidth Memory)は、メモリダイをロジック層の上に積層し、相互接続TSVチャンネルを持ち、GPUとの間にインターポーザーを介して接続され、X86ソケットよりも高い帯域幅を提供する。

- 主要なHBMサプライヤーはSK hynixであり、その後にSamsung、そしてMicronが続く。

- JEDECは、HBM標準を確認し発行しており、現行のHBM3E(拡張)がその5番目の規格である。

- Micronは、NvidiaのH200 Tensor Core GPUで使用するために24 GBのHBM3eチップを構築している。

- JEDECは、今年の終わりまでに完成したHBM4仕様を発行すると述べており、HBM4の特性が既に現れている。

- HBM4コントローラーは、HBM3E DRAMを制御できるようになる予定であり、HBM4は容量と帯域幅を向上させる。

- SK hynix、Samsung、Micronの間の激しい競争により、HBM4を使用したGPUシステムがより速くメモリにアクセスし、Gen AI LLM開発をより手頃な価格でスケーリングできる見込み。

この記事では、HBM4の開発や標準化に関する重要な情報が提供されています。GPU業界における技術革新と競争の激化が、AIや大規模言語モデルの開発にどのような影響を与えるか注目されます。特に、HBM4の登場により、GPUシステムがより高速なメモリアクセスを実現し、大規模なモデルの処理において重要な役割を果たすことが期待されています。

元記事: https://blocksandfiles.com/2024/07/19/hbm4s-accelerated-arrival/