- 10 Gb/sの完全なHWスタックUDP/IP送受信機

- 拡張MIPI CSI2シリアルビデオレシーバ、64ビット、8データレーン、4ピクセル/クロック

- 12ビット、640MspsデュアルチャネルIQ ADC IPコア

- Qualitas Semiconductorが8Gspsデータレートの5nm MIPI C-PHY IPを発表

- Skymizerがデバイス内LLM推論の画期的なLLMアクセラレータIPを発表

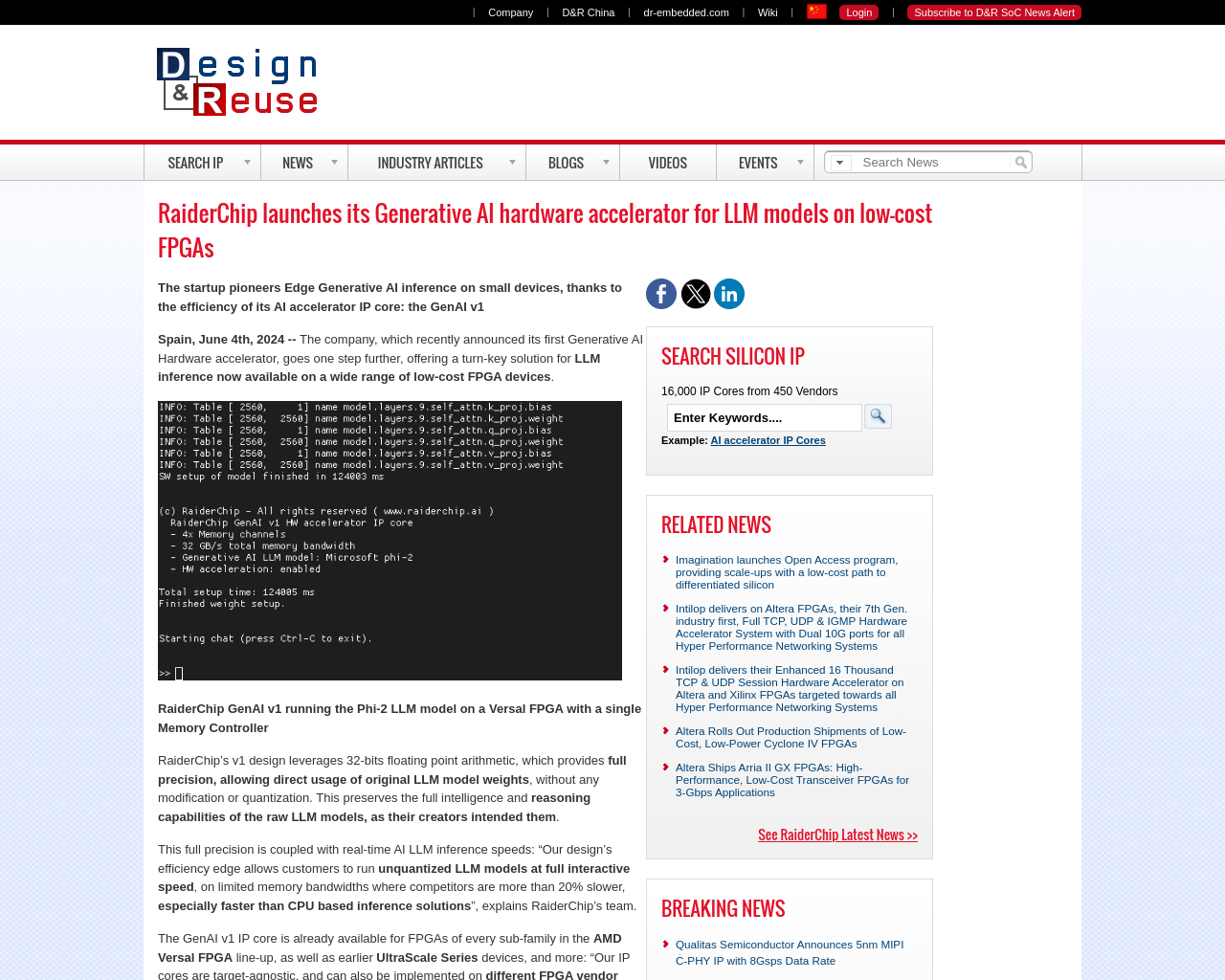

- RaiderChipが低コストFPGA上のLLMモデル向けにGenerative AIハードウェアアクセラレータを発売

- Positsおよび対数数値用の指数付き蓄積器を利用したProcrastination

- Portable StimulusとUVMレジスタモデルを使用したSoC統合テストの作成

- ネットワークオンチップ(NoC)設計における検証の重要性

- Codasip Studio Fusionによって可能になるソフトウェア/ハードウェアインターフェースの定義

- CASTのCEO、Dr. Nikos Zervasへのインタビュー

私の考え:Generative AIハードウェアアクセラレータの発展に興味深い記事であり、FPGAを使用したAI推論の新たな可能性が示唆されています。RaiderChipのGenAI v1 IPコアは、高速なLLM推論を提供するだけでなく、顧客の要件に合わせて柔軟に実装できる点が魅力的です。将来的なAIモデルやアルゴリズムの進化に対応するために、FPGAの利用は重要であり、既存のシステムのフィールドアップデートを可能にします。